Architektura MIPS

MIPS (Microprocessor without Interlocked Piped Stages) – architektura komputerowa (w szczególności procesor typu RISC) rozwijana przez firmę MIPS Technologies. Istnieje zarówno w wersji 32-, jak i 64-bitowej.

Procesory MIPS stanowiły do roku 2007 jednostkę centralną komputerów firmy SGI. Ponadto są szeroko stosowane w systemach wbudowanych (ang. embedded systems), w szczególności w urządzeniach opartych na systemie operacyjnym Windows CE. Są używane w routerach firmy Cisco i TP-Link, oraz w konsolach do gier takich jak Nintendo 64, Sony PlayStation, Sony PlayStation 2, Sony PSP. Szacuje się, że procesory MIPS stanowią jedną trzecią produkcji mikroprocesorów typu RISC.

Historia

W 1981 roku zespół kierowany przez Johna L. Hennessy’a na Uniwersytecie Stanforda rozpoczął pracę nad projektem, który dał w rezultacie pierwszą wersję procesora MIPS. Podstawowym założeniem projektu było zwiększenie wydajności poprzez wykorzystanie potokowego przetwarzania instrukcji, techniki znanej w tamtych latach, lecz trudnej w implementacji.

Podstawowym problemem w implementacji potokowości jest potrzeba stosowania blokad (ang. interlock), aby zapewnić by instrukcje wymagające wielu cykli zegarowych powstrzymały ładowanie nowych danych do potoku. Ustawianie blokad może być bardzo czasochłonne, dlatego uważano, że stanowią one podstawową barierę dla szybkości przetwarzania.

W architekturze MIPS wyeliminowano potrzebę stosowania blokad wymagając by każda instrukcja wykonywała się tylko w jednym cyklu zegarowym. Choć przy takim założeniu pomija się wiele użytecznych instrukcji (jak mnożenie i dzielenie, które wymagają wielu cykli) uważano, że wydajność może być znacznie poprawiona poprzez taktowanie zegarem o dużej częstotliwości.

W roku 1984 Hennessy był przekonany o przyszłych komercyjnych możliwościach architektury, dlatego opuścił Uniwersytet Stanforda zakładając firmę MIPS Computer Systems. Pierwszym projektem firmy był procesor R2000 ukończony w 1985 roku. Trzy lata później zakończono projektowanie ulepszonej wersji o oznaczeniu R3000. Były to procesory 32-bitowe różniące się od pierwszego akademickiego projektu dodaniem między innymi pełnych instrukcji mnożenia i dzielenia ze sprzętową implementacją większości blokad.

19 stycznia 2006 roku zmodyfikowany procesor MIPS R3000 pod nazwą Moongose-V poleciał w kierunku Plutona na pokładzie sondy New Horizons, jako procesor jej komputera pokładowego[1].

Architektura

Posiada 32 rejestry całkowitoliczbowe oraz 32 rejestry zmiennoprzecinkowe. Pierwszy rejestr całkowitoliczbowy jest pseudorejestrem zawierającym zawsze 0 ($zero), co w praktyce upraszcza wiele operacji. Trzydziesty pierwszy rejestr ($ra) całkowitoliczbowy jest adresem powrotu przy wywołaniach funkcji. Kolejne adresy są kładzione na stosie. To nietypowe rozwiązanie rozdziela operacje skoku powrotnego oraz pobranie adresu z pamięci, co skutkuje poprawą efektywności.

Inne rejestry nie są specjalne, są jednak tradycyjnie wykorzystywane jako:

| numer rejestru | kod rejestru w asemblerze | funkcja | odpowiednik w x86 |

|---|---|---|---|

| 1 | $at | zarezerwowana dla makr asemblera | brak |

| 2-3 | $v0-$v1 | rezultat wykonania funkcji | %eax i %edx |

| 4-7 | $a0-$a3 | argumenty do funkcji, ewentualne dalsze argumenty są odkładane na stosie | odkładane na stosie, w pewnych przypadkach, takich jak syscalle do jąder Linuksa czy Windowsa wykorzystywane są rejestry %eax, %ebx, %ecx, %edx, %esi, %edi, a w Linuksie 2.4 również %ebp |

| 8-15 oraz 24-25 | $t0-$t9 | ogólnego przeznaczenia, zachowywane przez wywołującego | %eax, %ebx, %ecx, %edx, %esi, %edi |

| 16-23 | $s0-$s7 | ogólnego przeznaczenia, zachowywane przez wywoływanego | niektóre z powyższych, zależnie od ustawień kompilatora |

| 26-27 | $k0-$k1 | wykorzystywane w procedurach przerwań | brak wyspecjalizowanych (wykorzystywane są zwykłe rejestry) |

| 28 | $gp | wskaźnik danych globalnych | brak, w trybie rzeczywistym jest do tego wykorzystywany rejestr segmentowy %ds |

| 29 | $sp | wskaźnik stosu | %esp |

| 30 | $fp lub $s8 | wskaźnik ramki | %ebp |

Dostępne wersje

- 1985: R2000

- 1988: R3000

- 1991: R4000

- 1992: R4400

- 1994: R4600, R8000

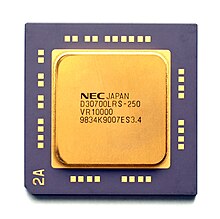

- 1995: R10000

- 1996: R5000

- 1998: R12000

- 2001: R14000

- 2002: R16000

- 2004: R16000A

Zobacz też

Przypisy

- ↑ Erik Kain, New Horizons Used A Playstation CPU To Fly By Pluto, Forbes [dostęp 2019-06-30] (ang.).

Linki zewnętrzne

- Strona firmowa MIPS Technologies

- MIPS Instructions. chaaban.info. [zarchiwizowane z tego adresu (2006-07-09)]. (fr.).

Media użyte na tej stronie

Autor: Konstantin Lanzet, Licencja: CC-BY-SA-3.0

CPU NEC VR10000 or µPD30700 (MIPS R10000).