Bramka NAND

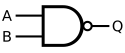

Bramka NAND (dysjunkcja) – bramka logiczna, która realizuje funkcję NAND. Znaczenie bramki przedstawia poniższa tablica prawdy:

| A | B | AB |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Bramki NAND wykorzystywane są – obok bramek NOR – w pamięciach flash. W stosunku do pamięci NOR pamięć NAND ma krótszy czas zapisu i kasowania, większą gęstość upakowania danych, korzystniejszy stosunek kosztu pamięci do jej pojemności oraz dziesięciokrotnie większą wytrzymałość.

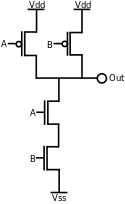

Bramki NAND wytwarzane są w technologii CMOS i TTL.

Sposoby zapisu bramki NAND

- – przedstawiana za pomocą symbolu ↑ (pionowa kreska „|” przechodząca przez symbol koniunkcji „^” dwóch argumentów, co oznacza jej logiczną negację)

- ⊼ – z użyciem symbolu ⊼ (U+22BC)

- – symbol oznacza koniunkcję (AND) natomiast kreska negację wyrażenia znajdującego się pod nią

- – jak wyżej z użyciem symbolu negacji ¬

- lub – zanegowany iloczyn logiczny

Wyrażanie funkcji boolowskiej w logice NAND

Jako że bramki logiczne NAND i NOR są tańsze w produkcji niż AND i OR, a ponadto zapewniają stałość amplitudy sygnału wyjściowego, w faktycznych układach cyfrowych są one stosowane częściej niż „zwykłe” AND i OR.

Korzystając z praw de Morgana, możemy każdą funkcję boolowską przekształcić tak, aby korzystała tylko z bramek NAND.

Negacja (NOT)

Korzystając z jednego z aksjomatów algebry Boole’a:

Zapisać możemy równoważnie, że:

Co jest negacją zmiennej wejściowej.

W innym zapisie:

⊼

Alternatywa (OR)

Skorzystamy tutaj z pierwszego prawa de Morgana, które w ujęciu algebry Boole’a przyjmuje postać:

Tak więc podając na wejście bramki NAND zanegowane zmienne wejściowe otrzymujemy alternatywę tych zmiennych, co wyraża poniższe równanie:

W innym zapisie:

⊼ ⊼ ⊼ ⊼

Koniunkcja (AND)

W przypadku koniunkcji jedynym wyjściem jest zanegowanie wyjścia bramki NAND, jako że podwójna negacja zmiennej daje tę samą zmienną.

W innym zapisie:

⊼ ⊼ ⊼ ⊼

Alternatywa wykluczająca (XOR)

Układ realizujący funkcję XOR z bramek NAND budujemy w oparciu o wyjściowe równanie funkcji XOR wykorzystując przekształcenia pokazane wyżej:

W innym zapisie:

⊼ ⊼ ⊼ ⊼ ⊼ ⊼ ⊼ ⊼ ⊼ ⊼ ⊼ ⊼

Zobacz też

Media użyte na tej stronie

Autor: Sakurambo, Licencja: CC-BY-SA-3.0

Simplified schematic of a TTL NAND gate made with npn transistors. Based on an earlier image created by RTC.

budowa bramki NAND CMOS.

A labelled MIL/ANSI symbol for an NAND gate. A and B are the inputs, Q is the output